@[toc]

ARM Cortex-M内核中DMA内存地址对齐的影响与效率权衡

1. 引言

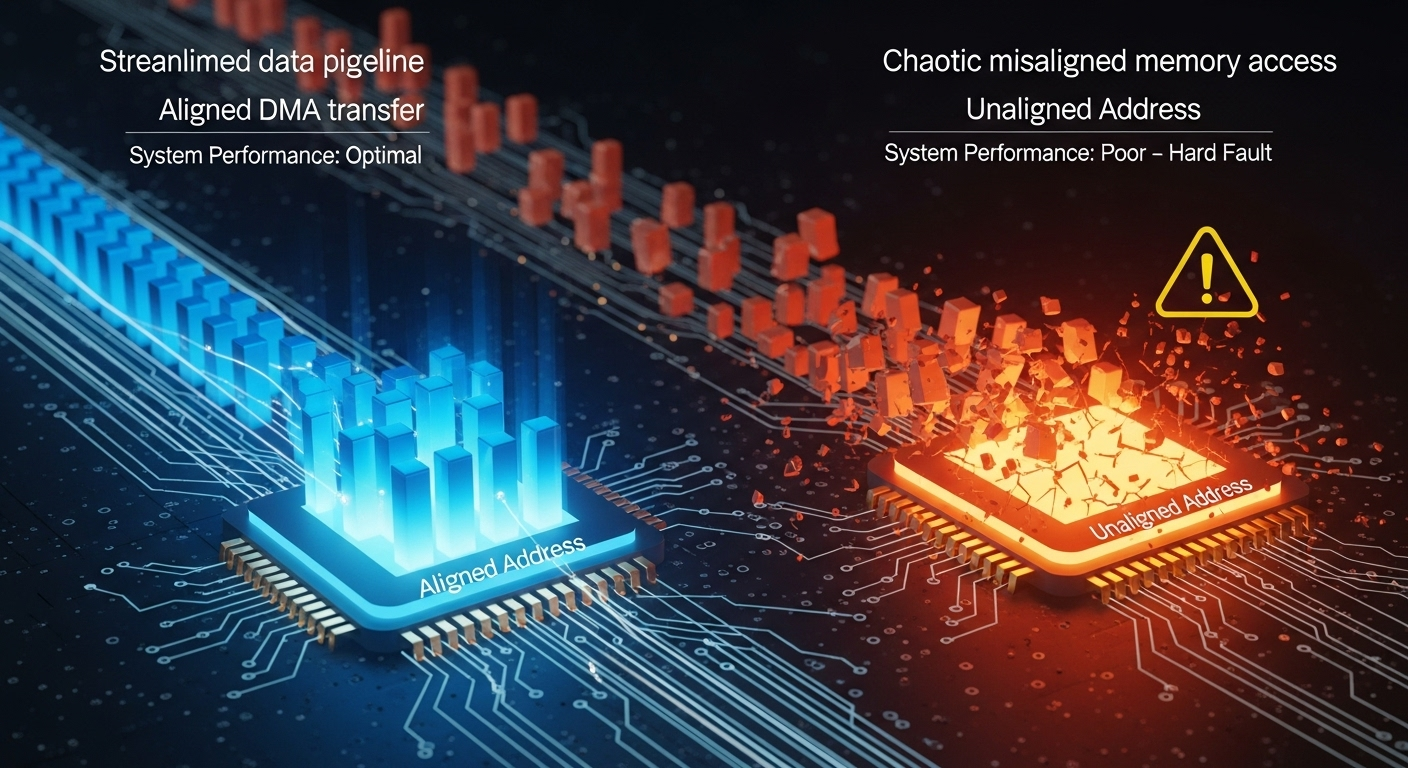

在基于ARM Cortex-M4/M7等高性能微控制器的嵌入式系统中,直接内存访问(DMA)是实现高数据吞吐量、降低CPU负载的关键技术。然而,DMA控制器的高效运作与其访问的内存地址是否对齐密切相关。本文旨在深度剖析当DMA访问未对齐内存地址时所引发的一系列问题,包括性能下降、硬件故障风险以及数据完整性问题。此外,本文将对“直接使用未对齐地址”与“预先拷贝至对齐缓冲区”这两种策略进行详尽的效率对比分析,以阐明在不同场景下的最优选择。

2. DMA与内存地址未对齐的定义

内存地址对齐是指一个数据的存储地址是其数据类型大小的整数倍。例如,一个32位(4字节)整数的地址若是4的倍数,则称其为地址对齐。DMA传输同样遵循此原则,其配置的数据宽度(通常为字节、半字或字)决定了理想的对齐边界。当DMA被配置为以字(4字节)为单位进行传输,但其源或目标内存地址不是4的倍数时,即构成了地址未对齐的DMA访问。

1 | graph TD |

3. 未对齐DMA访问对系统的核心影响

在ARM Cortex-M4/M7架构上,未对齐的DMA访问会直接或间接地导致多种负面后果。

3.1 性能显著下降

这是最直接的影响。尽管Cortex-M内核在一定程度上支持非对齐的内存加载/存储操作,但这是以牺牲执行效率为代价的。硬件会自动将一次未对齐的总线事务分解为多次对齐的、更小粒度的访问。

- 增加总线周期: 一次4字节的未对齐访问可能会被硬件拆分为两次或多次1字节/2字节的对齐访问。这会引入额外的总线周期,对于Cortex-M4/M7,通常会给单次访问带来1至2个时钟周期的固定开销。

- 累积效应: 在DMA传输中,这种单次访问的性能损失会被数据总量放大。对于一个大数据块的传输,持续的未对齐惩罚将导致整体数据传输带宽显著低于理论峰值。

1 | graph TD |

3.2 引发硬件故障 (Hard Fault)

在特定条件下,未对齐访问并非仅仅是性能问题,而是会导致系统级的严重错误。

- 访问受限的内存区域: 当DMA访问的内存区域被内存保护单元(MPU)配置为“设备内存”(Device Memory)或“强序内存”(Strongly-ordered Memory)时,任何非对齐的访问都是被严格禁止的。此类访问会立即触发一个精确的总线错误(Bus Fault),进而导致系统进入Hard Fault中断服务程序,通常表现为系统挂起或复位。

- 未定义的DMA行为: 某些DMA控制器的硬件实现可能并未对所有未对齐场景进行定义。提供一个未对齐的地址而配置一个较宽的数据宽度,可能导致DMA控制器进入未定义状态,从而产生不可预测的数据损坏或系统锁定。

3.3 Cortex-M7特有的缓存一致性问题

Cortex-M7内核引入了数据缓存(D-Cache),这使得地址对齐问题变得更为复杂。缓存操作(如清理或作废)的基本单位是缓存行(Cache Line),在Cortex-M7上通常为32字节。

- 管理效率: 当DMA缓冲区地址与缓存行边界(32字节的倍数)对齐时,缓存维护操作最为高效。

- 管理复杂性: 未对齐的缓冲区会使缓存管理变得复杂。一个缓冲区可能跨越多个缓存行,且其起始和结束地址不与行边界重合,这要求更精细、更耗时的缓存操作来确保CPU视图与内存视图的一致性,否则极易在CPU与DMA之间共享数据时出现数据陈旧或丢失的问题。

4. 效率权衡:“直接DMA” vs “预拷贝+DMA”

面对未对齐的数据源,开发者面临一个抉择:是直接让DMA处理未对齐地址,还是先由CPU将数据拷贝到一个对齐的缓冲区再启动DMA?

4.1 两种方案的时间成本构成

方案A:直接进行未对齐DMA (T_direct)

- CPU成本: 几乎为零,仅需配置和启动DMA。

- DMA成本: 传输时间因持续的未对齐惩罚而延长。

- 时间公式 (概念性):

T_direct = N * (T_base_transfer + T_unalign_penalty)N: 传输的数据单元总数。T_base_transfer: 一次对齐传输的基础时间。T_unalign_penalty: 每次传输因未对齐产生的额外时间。

方案B:CPU预拷贝至对齐缓冲区 + 对齐DMA (T_copy_then_dma)

- CPU成本: 执行

memcpy操作将数据从源地址拷贝到对齐缓冲区所需的时间。 - DMA成本: DMA以最高效率运行,无任何未对齐惩罚。

- 时间公式 (概念性):

T_copy_then_dma = T_memcpy + (N * T_base_transfer)T_memcpy: CPU执行内存拷贝的总时间。

- CPU成本: 执行

1 | graph TD |

4.2 效率对比与数据量的决定性作用

两种方案的优劣取决于 T_memcpy 与 N * T_unalign_penalty 的大小关系。

- 小数据量场景: 当

N非常小时(如几十字节),N * T_unalign_penalty的累积惩罚不明显,而T_memcpy的固定开销(如函数调用、地址计算等)相对突出。此时,直接进行未对齐DMA可能更快。 - 大数据量场景: 当

N非常大时(符合“一次性发送大量数据”的场景,如数千至数万字节),N * T_unalign_penalty会被急剧放大,成为总时间的主要瓶颈。与之相比,T_memcpy虽然是一项前期投入,但其单位字节的拷贝效率非常高且稳定。在这种情况下,一次性的T_memcpy开销远小于持续的DMA性能损失。因此,对于大数据块,“预拷贝+DMA”方案的总耗时几乎总是更短。

4.3 内存资源占用的考量

关于额外内存占用的担忧:“预拷贝+DMA”方案的明确缺点是需要额外分配一块与传输数据同样大小的、地址对齐的缓冲区。这会增加系统的RAM占用,降低内存利用率。在内存资源极其紧张的系统中,这可能是一个不可接受的折衷。

5. 结论与最佳实践

影响总结: 在ARM Cortex-M4/M7平台上,DMA访问未对齐内存地址会造成显著的性能下降,并可能因访问受限内存区域而引发致命的硬件故障。对于Cortex-M7,还会增加缓存一致性管理的复杂性。

效率权衡:

- 对于大数据块传输,从总时间效率和系统稳定性的角度出发,“CPU预拷贝至对齐缓冲区 + 对齐DMA”是更优的选择。它以一次性的CPU开销和额外的内存占用为代价,换取了DMA传输的最高效率和系统的健壮性。

- 对于小数据块且实时性要求极高的场景,如果能够确保不触发硬件故障,直接进行未对齐DMA可能是可行的,但这需要仔细的性能评估和风险分析。

最佳实践:

- 编译时对齐: 在设计阶段,应尽可能通过编译器指令(如

__attribute__((aligned(N))))静态地定义DMA缓冲区,使其地址天生对齐。这是解决问题的最根本、最高效的方法,因为它避免了运行时的任何额外开销。 - 动态对齐分配: 若必须动态分配,应使用支持对齐分配的内存函数(如

aligned_alloc)或自定义的内存池。 - 合理配置MPU: 善用内存保护单元(MPU)来管理内存区域的属性(如配置为“普通内存”以容忍非对齐访问,或配置为“非缓存”以规避缓存一致性问题),可以从硬件层面消除许多潜在的故障点。

- 编译时对齐: 在设计阶段,应尽可能通过编译器指令(如

最终,选择何种策略取决于应用对时间效率、内存效率和系统稳定性三者之间优先级的综合考量。