[TOC]

STM32系列微控制器DMA寄存器写入失败的解决方法

摘要:

本文旨在深入分析在STM32系列微控制器嵌入式系统开发中,导致直接内存访问(DMA)控制器相关寄存器,特别是控制寄存器(DMA_SxCR),写入操作失败的根本原因。文章首先阐明,外设时钟的缺失是导致寄存器无法访问的绝对前提条件。其次,文章将探讨在运行时对一个已使能的DMA数据流进行配置修改而导致写入被硬件忽略的更常见情况。本文通过结构图、流程图和代码实例,系统性地阐述了该问题的诊断方法和标准的解决方案,旨在为开发者提供一套严谨的规范,以确保DMA功能的稳定性和可靠性。

关键词: STM32; DMA; 寄存器写入失败; 外设时钟; AHB总线; DMA_SxCR

引言

直接内存访问(DMA)控制器是STM32微控制器中一个至关重要的外设,它能够在不占用中央处理器(CPU)的情况下,高效地实现外设与内存、内存与内存之间的数据传输,极大地提升了系统的数据吞吐能力和CPU效率。在进行DMA相关功能的开发与调试时,开发者偶尔会遇到一个棘手的问题:对DMA流(Stream)的配置寄存器(例如 hdma->Instance->CR)执行赋值操作后,通过调试器观察发现寄存器的值并未按预期改变,即写入操作失败。

此类问题会直接导致DMA传输无法启动或行为异常。经过对STM32硬件架构的深入分析,可以确定该问题的首要和根本性原因在于:目标DMA控制器的AHB总线时钟未被使能。在此时钟缺失的前提下,该外设的所有逻辑电路,包括响应总线写操作的接口逻辑,均处于非工作状态,任何对其寄存器的访问都将无效。

第一章:外设寄存器访问的必要前提——总线时钟

1.1 STM32总线架构与外设时钟

STM32微控制器采用先进的哈佛架构,并通过一个复杂的多层总线矩阵连接高速的AHB(Advanced High-performance Bus)总线和低速的APB(Advanced Peripheral Bus)总线。DMA控制器(如DMA1, DMA2)通常挂载在高性能的AHB1总线上,以便快速访问内存和大部分外设。

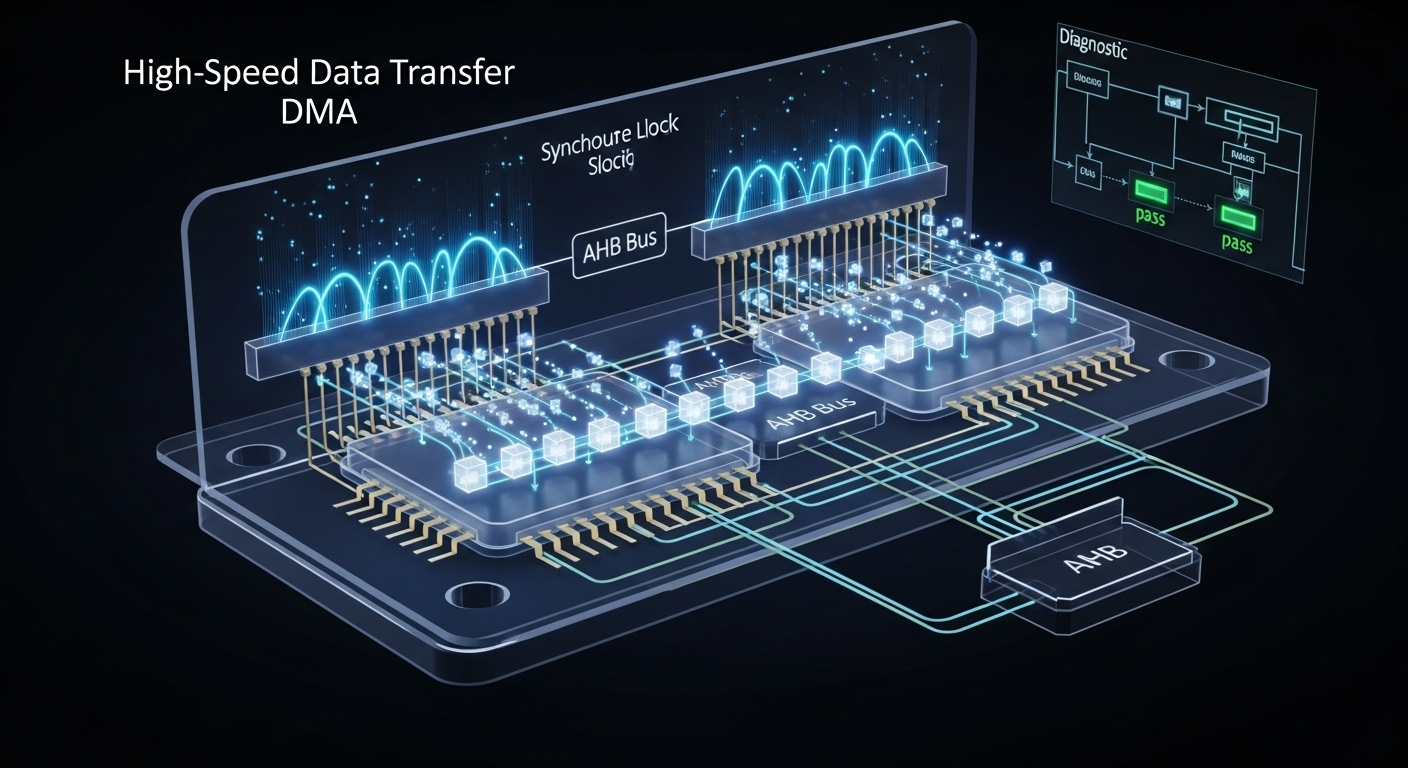

图 1:STM32总线架构简化示意图

如图1所示,CPU对任何外设寄存器的写操作,其指令和数据都需要通过总线矩阵和相应的AHB/APB总线,最终到达目标外设的接口逻辑。外设的内部逻辑电路,包括其寄存器组,需要一个稳定的时钟信号来驱动状态机、锁存数据和执行操作。此时钟由复位和时钟控制器(RCC)统一管理和分配。

1.2 时钟缺失对寄存器写入的影响

在STM32的设计中,为了实现低功耗管理,所有外设的时钟在系统复位后默认处于关闭状态。开发者必须在代码中通过配置RCC相关寄存器,显式地为需要使用的外设使能时钟。

如果DMA2的时钟(RCC_AHB1ENR寄存器中的DMA2EN位)未被置1,那么DMA2控制器的物理电路将不会获得工作所需的时钟信号。在这种状态下:

- 接口逻辑不工作:响应AHB总线读写周期的逻辑单元处于非活动状态。

- 写入操作被忽略:当CPU通过总线发出对DMA2寄存器地址空间的写命令时,由于DMA2的时钟门控(Clock Gating)电路是关闭的,写信号无法触发寄存器锁存器的数据更新。

- 读取操作返回固定值:同理,读取DMA2寄存器的值通常会返回总线的默认值(例如

0x00000000),而非寄存器的真实内容。

代码实例:

在进行任何DMA2寄存器操作之前,必须执行以下或等效的使能时钟操作(以HAL库为例):

1 | // 在所有DMA2相关配置之前,必须先使能其时钟 |

图 2:RCC至DMA2的时钟路径示意图

图2清晰地展示了时钟信号从源头(如HSI/HSE)经过RCC模块,最终通过AHB1总线使能寄存器分配给DMA2控制器的路径。任何环节的中断都将导致外设功能失效。

第二章:运行时写入失败的常见原因——修改已使能的DMA流

在确保DMA时钟已正确使能后,如果在程序运行过程中仍然出现DMA_SxCR寄存器写入失败,那么其原因几乎总是试图修改一个已经被使能(EN位为1)的DMA流。

2.1 DMA流控制寄存器(DMA_SxCR)与硬件互锁机制

DMA_SxCR寄存器的第0位是流使能位(EN)。根据STM32参考手册的规定,为保证数据传输的完整性和一致性,一旦EN位置1,DMA流进入活动状态,此时硬件会锁定DMA_SxCR寄存器中的绝大部分配置位(EN位自身除外,可以被清零以禁用流),以及DMA_SxNDTR(传输数量)、DMA_SxPAR(外设地址)、DMA_SxM0AR(内存地址0)等关键配置寄存器。

这种硬件互锁机制是防止在数据传输过程中,因配置突变而导致数据损坏或系统崩溃的关键设计。因此,任何在DMA_SxCR.EN == 1的情况下对这些寄存器的写入操作都将被硬件自动忽略。

2.2 正确的DMA流重配置流程

若需在运行时动态修改一个DMA流的配置(例如改变传输长度或内存地址),必须严格遵循“先禁用,再配置,后使能”的原子操作序列。

代码实例(直接寄存器操作):

1 | // 假设dma_stream指向DMA2_Stream2 |

第三章:综合诊断与最佳实践

3.1 诊断流程

当遇到DMA寄存器写入失败时,应遵循以下诊断流程进行排查。

3.2 最佳实践

- 初始化优先:在

main()函数的开始部分,或在MX_DMA_Init()函数的第一行,务必确保对应DMA控制器的时钟已经被使能。 - 遵循原子操作:任何对已启动DMA流的修改,都必须严格遵循图3所示的“禁用-配置-使能”流程。强烈推荐将此流程封装成一个独立的函数,以保证操作的原子性。

- 善用HAL/LL库:STM32的HAL库和LL库函数(如

HAL_DMA_Start(),HAL_DMA_Abort())内部已经封装了对DMA状态和寄存器操作的正确逻辑。优先使用这些库函数可以有效避免直接寄存器操作带来的风险。 - 注意初始化顺序:确保DMA的初始化(

MX_DMA_Init())和使用DMA的外设(如UART, ADC)的初始化具有正确的依赖关系。通常应先初始化DMA,再初始化依赖于它的外设。

结论

STM32中DMA寄存器写入操作的失败,其根源可归结为两个层面:静态初始化层面和动态运行时层面。

在静态初始化层面,未使能DMA外设对应的AHB总线时钟是导致一切访问失败的根本前提。这是硬件工作的物理基础,必须在所有寄存器配置之前得到满足。

在动态运行时层面,对一个已处于活动状态的DMA流进行配置写入,会因硬件保护机制而导致写入操作被忽略。这是最常见的编程错误,必须通过严格的“禁用-配置-使能”操作序列来规避。

通过理解上述两种机理,并遵循本文提出的诊断流程和最佳实践,开发者可以系统性地预防和解决DMA寄存器写入失败的问题,从而保障嵌入式系统数据传输的稳定与高效。